Sommaire du Guide Technique

- 1. Introduction : Le MC1000 et le format Type 10

- 2. Architecture Silicium : La révolution Panther Lake

- Hybridation P/E/LPE et gestion des threads

- GPU Intel Arc & capacités GPGPU

- NPU intégré : L'accélération IA native

- 3. Sous-système Mémoire et Bande Passante

- 4. Connectivité et Interfaces Industrielles

- Ethernet 2.5 GbE et support TSN

- Allocation PCIe et USB

- Affichage et HMI 4K

- 5. Firmware, Management et Sécurité (TPM 2.0)

- 6. Guide de Gestion Thermique

- 7. Spécifications Techniques Détaillées (Tableau)

- 8. Comparatif des Variantes Processeurs

- 9. Recommandations d'Intégration et Checklist

- 10. Contact et Support Spécifique (+datasheet)

Le guide d’intégration complet — COM Express Type 10 (MC1000)

Ce guide technique vise les ingénieurs en charge du design‑in : il détaille l’architecture silicium, le sous‑système mémoire et bande passante, la connectivité et interfaces industrielles, la gestion thermique, les contraintes PCB et mécaniques, la validation et la mise en production. L’objectif est de fournir suffisamment de matière pour concevoir une carte porteuse robuste et optimiser les performances de la plateforme COM Express Type 10 (MC1000).

Résumé rapide

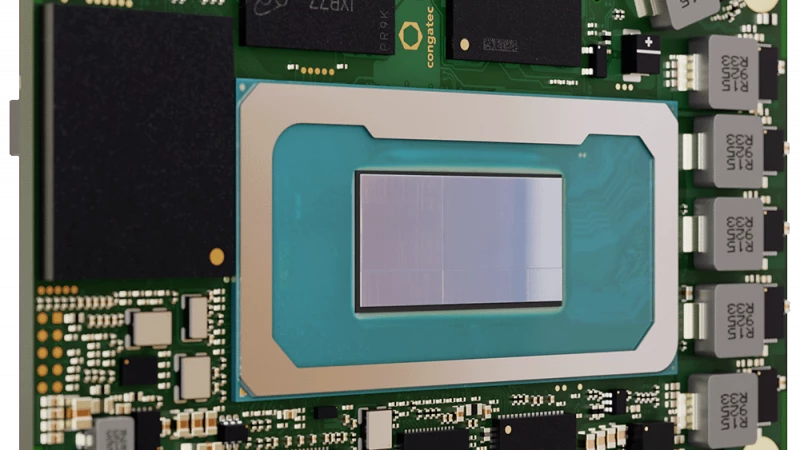

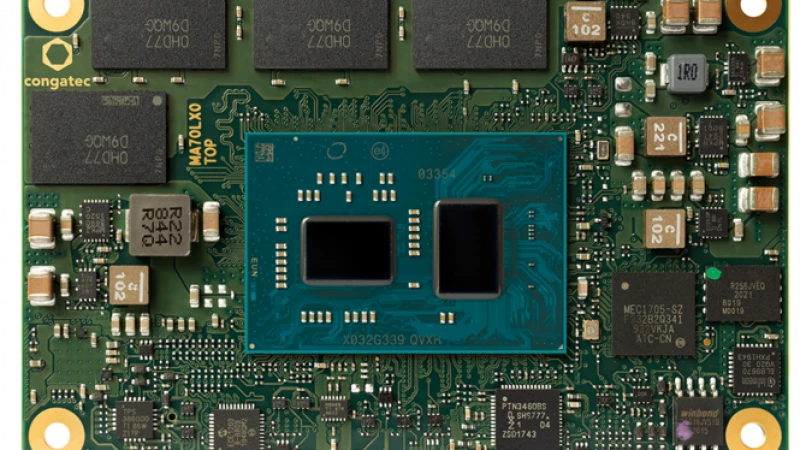

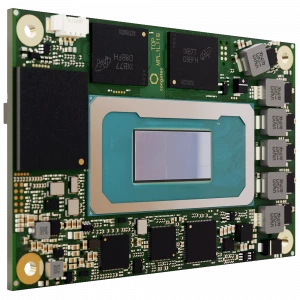

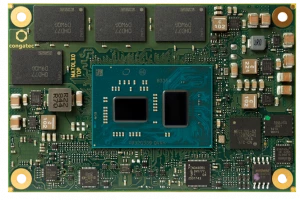

Le MC1000 est un module COM Express Mini (Type 10) au format 55 × 84 mm intégrant les processeurs Intel Core Ultra (Panther Lake). Il combine CPU hybride (P‑cores/E‑cores/LPE‑cores), GPU Intel Arc (selon SKU) et NPU intégré (≈ 50 TOPS), avec LPDDR5x soudée (jusqu’à 32 GB) et interfaces NVMe, PCIe, USB, SATA et 2.5GbE. Ce guide couvre les implications techniques et les meilleures pratiques d’intégration.

1 - Architecture silicium — ce que les ingénieurs doivent savoir

a) Hybridation P/E/LPE : gestion fine des performances et consommation

- L’architecture combine des cœurs Performance (P), Efficiency (E) et Low‑Power Efficient (LPE). Le scheduler OS/hypervisor doit être conscient de cette hiérarchie pour assigner correctement les threads : charges temps réel/latence sur P‑cores, tâches de fond sur E/LPE.

- Impacts pratiques :

- Privilégier l’affinité thread/core pour charges AI temps réel (p.ex. dédier P‑cores aux threads critiques).

- Adapter les politiques d’ACPI et C‑states pour éviter latence lors des wakeups (surtout sur I/O temps réel).

b) Cache, interconnect et coherency

- Grandes tailles de cache L3 (jusqu’à 18 MB selon SKU) : réduit la pression mémoire pour charges ML/vision, mais attention aux working sets > cache.

- Interconnect interne (ring/mesh selon implémentation) : la latence entre cœurs et NPU/GPU influence fortement les performances de fusion CPU‑NPU.

c) GPU Arc & capacités GPGPU

- GPU Intel Arc (jusqu’à 12 Xe cores sur les variantes hautes) offre capacité GPGPU pour preprocessing et certaines inferérences.

- Règles : dimensionner la bande passante mémoire (LPDDR5x) et veiller aux échanges CPU↔GPU (PCIe ou interconnect interne) selon le workflow.

d) NPU intégré

- NPU ~50 TOPS : conçu pour l’inférence optimisée (INT8/INT4/quantized ops).

- Pour atteindre les ~180 TOPS « plateforme », combiner NPU + GPU + CPU. L’orchestration des workloads (où exécuter quelle partie d’un modèle) doit être testée en profilage réel.

2 - Sous‑système mémoire et bande passante

a) LPDDR5x soudée — avantages et contraintes

- Jusqu’à 32 GB LPDDR5x à ~8533 MT/s : excellente bande passante mémoire et faible latence relative.

- Soudée (PoP non applicable) : réduit latence d’accès et risques mécaniques mais interdit l’upgrade en production.

- In‑band ECC disponible sur certaines variantes : important pour applications critiques (médical, industriel).

b) Dimensionnement bande passante pour IA/vision

- Le couple NPU/GPU est gourmand en bande passante : concevoir pipelines qui minimisent transferts redondants mémoire ↔ NPU.

- Utiliser SRAM caches locaux sur carrier (si nécessaire) pour buffering caméra haute cadence avant traitement NPU.

c) Latences et contention

- Contention possible entre NVMe, GPU et NPU si tous accèdent intensément la mémoire.

- Priorisation QoS : si l’architecture matérielle/firmware le permet, configurer priorités pour trafic temps réel (DMA channels, AXI QoS).

3 -Stockage et sous‑système NVMe / SATA

- NVMe intégré : meilleure option pour performance et endurance. Pour logs à haute fréquence ou base de données locale, sélectionner SSDs étalonnés pour writes intensifs.

- SATA (2 ports) disponible : utile pour systèmes legacy ou stockage rotatif/SSD SATA.

- Recommandation : isoler les canaux NVMe par plan de masse et prévoir power‑rails régulées pour éviter brown‑outs sur pics d’I/O.

4 -Connectivité et interfaces industrielles

a) Ethernet 2.5 GbE et TSN

- Contrôleur 2.5GbE (Intel i226) : bon compromis débit/empreinte. TSN (Time Sensitive Networking) optionnel pour trafic déterministe (contrôle moteur, robotique).

- Design board : prévoir magnetics et filtres EMI adéquats ; respecter recommandations i226 pour layout differential pairs, common mode choke et AC coupling.

b) PCIe et allocation lanes

- 4 lanes PCIe disponibles pour expansion (Gen3 typiquement) : utilisées pour accélérateurs, NICs ou interface NVMe additionnelle.

- Lors du routage :

- Respecter impédance 85/100Ω différentielle selon stackup.

- Length match les paires entre endpoints critiques.

- Minimiser vias sur differential pairs ; éviter stubs.

c) USB / UART / GPIO / I²C / SMBus

- 2 × USB 3.2 et 8 × USB 2.0 : planifier hubs USB sur carrier si besoin d’augmenter ports USB3.

- 2 UART RX/TX : souvent critiques pour debug/boot loader ; prévoir accès physique ou header dédié.

- SMBus / I²C : utile pour gestion capteurs thermiques, alimentation PMIC et BMC.

d) Vidéo / HMI

- DDI (DP++), eDP / LVDS : support de 2 écrans 4K indépendants.

- eDP single channel pour panels internes ; LVDS pour legacy. Assurer intégrité signal (eDP lanes length matching) et planifier backlight control (PWM) via BIOS/UEFI.

5 - Firmware, management et sécurité

a) UEFI, BMC léger et watchdog

- AMI Aptio UEFI : possibilités OEM (OEM logo, CMOS defaults, LCD control, POST redirection). Intégrer scripts de recovery (USB ou serial) pour field recoveries.

- Module Management Controller (BMC-lite) : watch‑dog multistage, board information, statistics, POST code redirection, power loss control. Exposer diagnostics via SMBus/I²C.

b) Sécurité matérielle

- TPM 2.0 disponible : activer secure boot, measured boot et storage encryption.

- Gestion clés : prévoir politique de provisioning du TPM en production (clé OEM vs key injection client).

c) OS & hypervisors

- Support Windows IoT / Windows 11 / Linux / Yocto / RTOS / hypervisor temps réel. Pour RT/soft‑PLC, valider scheduler et latences sous charge NPU/GPU.

6 -Gestion thermique — bonnes pratiques d’ingénierie

a) Budget thermique et dissipation

- TDP processeur ≈ 25 W (varie selon SKU). Avec GPU/NPU en charge, budget thermique augmente localement.

- Solutions mécaniques : heatspreader (HSP‑B, HSP‑T), conduction via standoffs, radiateur additionnel ou ventilation forcée selon enveloppe du produit.

b) Conception du heat path

- Coupler module → heatspreader via thermal pads à faible résistance thermique (0.5–1 mm typiques).

- Fixation mécanique : HSP‑B (standoffs 2.7 mm bore) vs HSP‑T (M2.5 fileté) — respecter les trous et couples de serrage pour éviter contraintes BGA.

- Si conduction à la chassis : prévoir grande surface et éventuellement caloducs.

c) Monitoring et thermal management

- Exposer capteurs thermiques (on‑die ou module) vers l’OS via SMBus / ACPI.

- Implémenter politiques d’empilement : fan curves, dynamic voltage/frequency scaling (DVFS), thermal zones ACPI.

- Test : thermal soak tests, performances soutenues (sustained workload) pour définir throttling points.

7 - Contraintes PCB & routage — checklist détaillée

a) Alimentation & sequencing

- Alimentation principale 8.5–20 V → PMIC sur carrier pour rails internes (VCC_CORE, VCC_GFX, VCC_SRAM…).

- Respecter séquence boot (power‑good signals) ; prévoir supervision rails et reset control pour sécurité.

- Découplage : proximité condensateurs céramiques MLCC près d’alimentation critique, plane de puissance dédié.

b) Intégrité signal & high‑speed routing

- Stackup PCB recommandé : 6–8 couches minimum pour séparer power/ground et high speed.

- PCIe/USB/2.5GbE : règle d’impédance, length matching, via usage limité et back drilling si nécessaire.

- EMI : vias stitching, ground pour return paths, partitioning des power islands.

c) Connecteurs & keepouts

- Respecter zone keepout sous module (encombrement BGA, composants sur carrier sous heatspreader).

- Edge connector COM Express Type 10 : vérifier brochage, fixation et insertion force ; prévoir retenues mécaniques.

d) Mécanique et fiabilité

- Fixations mécaniques via standoffs : utiliser les trous et empreintes correspondantes ; éviter contraintes mécaniques excessives sur BGA à l’assemblage.

- Conformal coating : si besoin (milieu humide), prendre en compte dissipation thermique et outgassing.

- Choix de matériaux : coefficients d’expansion compatibles entre carrier et module.

8 -Tests de validation et qualification

- Signal integrity : eye diagrams, BER pour PCIe/USB/Ethernet.

- Thermal : thermal imaging sous charge, thermal cycling (-40/+85 selon besoin), steady state power.

- Vibration & choc : tests selon IEC 60068 / MIL-STD si requis.

- EMI/EMC : tests de rayonnement et immunité selon application (CE, FCC, EN).

- Stress IO : endurance NVMe, write amplification tests, stress sur bus CAN/fieldbuses si présents.

9 - Fabrication & production

- Assemblage : module soudé au carrier via edge connector — vérifier process de pick & place du carrier autour du connecteur.

- Tests en production : boundary scan / JTAG, tests de continuité rails, test d’intégrité mémoire.

- Field service : prévoir méthode de recovery (USB boot, serial console) et pièce de rechange (modules pré‑programmés).

Checklist design‑in (à imprimer pour l’équipe)

- Sélection SKU (Ultra 5/7/9/X9) selon besoin GPU/NPU et budget thermique

- Définir capacité mémoire + ECC requirement

- Choisir solution thermal (HSP‑B / HSP‑T / ventilateur)

- Planifier NVMe sizing & endurance

- Déterminer allocation PCIe lanes et hubs USB si nécessaire

- Layout : stackup, impedance control, length matching

- Alimentation : PMIC, decoupling, sequencing

- Firmware : secure boot + TPM provisioning

- Validation : SI, thermal soak, EMC, vibration

- Documentation : BOM, assembly drawings, torque settings

10 - Spécifications techniques (récapitulatif)

| Caractéristique | Spécifications Techniques |

|---|---|

| Format | COM Express Mini (Type 10), 55 x 84 mm |

| Processeurs | Intel® Core™ Ultra Series 3 (Panther Lake) |

| Architecture | Hybride (P‑cores, E‑cores et LPE‑cores) |

| Mémoire vive | Jusqu'à 32 Go LPDDR5x soudée (8533 MT/s) |

| Accélération IA | NPU intégré (50 TOPS) / Jusqu'à 180 TOPS au total |

| Graphismes | Intel® Arc™ Graphics (jusqu'à 12 Xe cores) |

| Stockage | Support NVMe SSD embarqué jusqu'à 1 To |

| Réseau | 1x 2.5 GbE (i226) avec support TSN |

| Affichage | 1x DDI (DP++), 1x eDP/LVDS (2 écrans 4K indépendants) |

| E/S Haute Vitesse | 4x PCIe Gen 3, 2x USB 3.2, 8x USB 2.0 |

| Stockage Classique | 2x SATA III (6 Gb/s) |

| Sécurité | Trusted Platform Module (TPM 2.0) |

| Alimentation | Large plage 8.5V – 20V, ACPI 6.0 |

11 - Tableau comparatif des variantes processeurs

| Modèle | Cœurs (P+E+LPE) | Fréquence Max | Cache L3 | GPU (Xe cores) | NPU | Usage typique |

|---|---|---|---|---|---|---|

| Ultra X9 388H | 4 + 8 + 4 = 16 | 5.1 GHz | 18 MB | Arc B390 (12 Xe) | 50 TOPS | IA embarquée intensive, vision complexe |

| Ultra 9 386H | 4 + 8 + 4 = 16 | 4.9 GHz | 18 MB | Intel Graphics (4 Xe) | 50 TOPS | CPU/GPU high perf, multitâche |

| Ultra 7 356H | 4 + 8 + 4 = 16 | 4.7 GHz | 18 MB | Intel Graphics (4 Xe) | 50 TOPS | équilibré, traitement temps réel |

| Ultra 5 325 | 4 + 0 + 4 = 8 | 4.5 GHz | 12 MB | Intel Graphics (4 Xe) | 50 TOPS | basse consommation, applications légères |

Ressources utiles

- Téléchargement fiche technique (datasheet) : Datasheet PDF — MC1000 (COM Express Type 10)

Besoin de modules COM Express Type 10 ?

CONTACT : k.gouacide[at]tokhatec.com